## PICO1TRCL Description

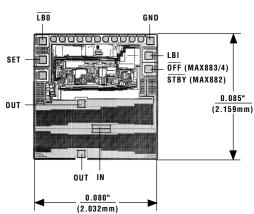

The PICO1TRCL is a low-cost microcontroller development board that is compatible with the Arduino development tools. The board is 2.1" x 1.65" and all the I/O pins from the ATmega328 are brought out on 2 rows of 14 pins (300mil spacing).

## Features

- 2.1" x 1.65"

- Replaceable and upgradeable CPU

- Compatible with the Arduino development tools.

- ATmega328P running at 12MHz

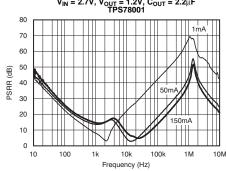

- Dual output voltage LDO 3.3V/2.2V

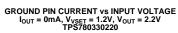

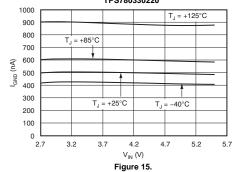

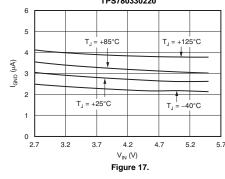

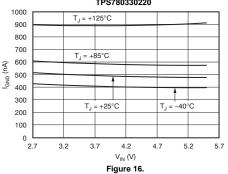

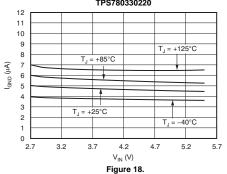

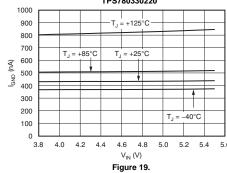

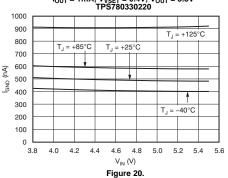

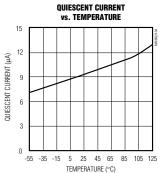

- Low LDO  $I_Q$  900nA (SMD), 15 $\mu$ A (TH)

- $\bullet$  0.6" x 0.6" prototyping area

- Real-time clock with two alarms (I2C interface)

- Two rows of 14 pins (300mil spacing) with all ATmega328 I/O functions.

- Six pin header for FTDI TTL-232R-3V3 cable.

- Debug LED that can be jumpered to Pin 7 or disconnected.

- A/D reference supply filtered per Atmel specification.

- Reset circuit per Atmel specification.

## 1 Assembling the PICO1TRCL

Semiconductors are electrostatic-sensitive devices. Proper ESD handling precautions need to be taken to avoid damage.

Do not cut any of the U1 socket pins until you have determined which pins are needed in your application. All of the PICO1TRCL I/O pins are the U1 socket pins. See subsection 1.7 for pin removal information.

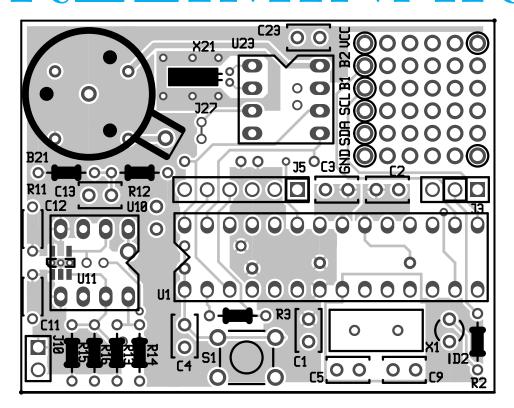

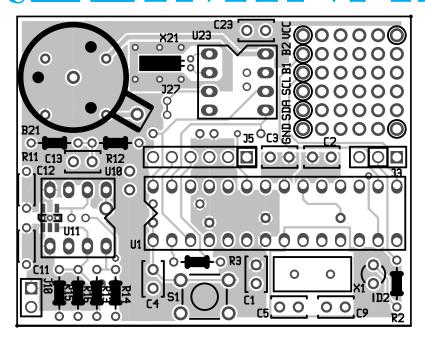

The Bill of Materials (BOM) and Component List are in section 6. For full page assembly drawings see Figure 1 (top) and Figure 2 (bottom).

There are two different BOMs and Component Lists – one for the TH kit and one for the SMD kit. The PCB and assembly drawings are common to both kits.

## 1.1 Bottom Side Components

• D1

Line the cathode marking on D1 with the cathode marking on the silkscreen

• D21, D22

Line the cathode marking of D21,D22 with the cathode marking on the silkscreen

• L1

The value of inductor L1 is not critical. Kits will contain an inductor with a value between  $10\mu H$  and  $20\mu H$

- R1, R22, R23 10KΩ (brown, black, black, red, brown)

- C6

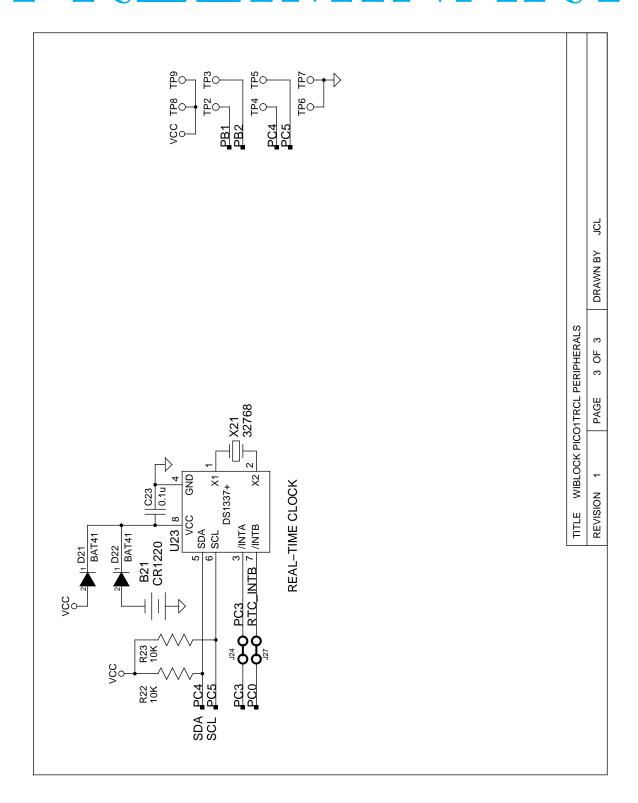

## 1.2 Real-time Clock Circuit Assembly

- X21 crystal

- U23 socket

- B21 battery holder

- C23

## 1.3 Power Supply Circuit Assembly

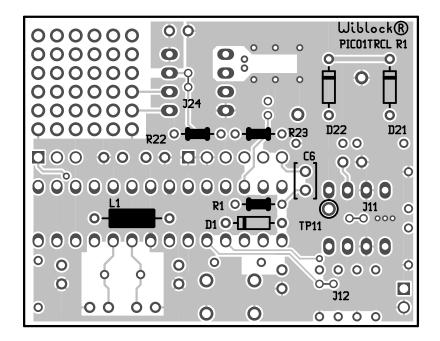

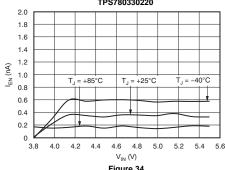

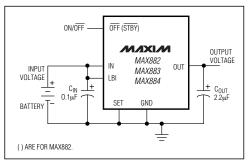

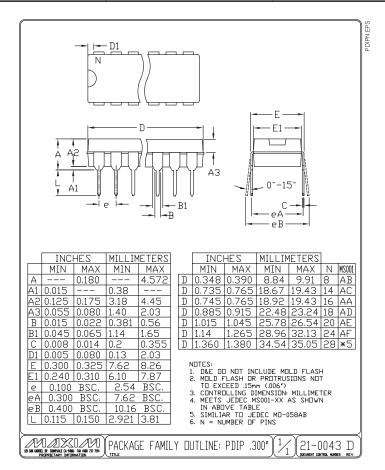

There are two versions of the PICO1TRCL kit – SMD and TH. The SMD kit features a very low  $I_Q$  linear regulator in an SMD package (SOT23-5). The TH kits uses a linear regulator in a DIP8-300 package. Both kits use the same PCB.

For the TH kit follow the instructions in subsubsection 1.3.1. For the SMD kit follow the instructions in subsubsection 1.3.2.

Since most applications will never disable the LDO it is recommended that R15 be replaced with a jumper wire, R16 be left open and jumper J12 be cut to free up the AT-mega328P line connected to STBY (EN on the SMDLDO). These changes should be performed prior to adding the LDO components.

## 1.3.1 TH LDO Assembly

Solder the top side components:

- C11, C12, C13

- R11

845KΩ (gray, yellow, green, orange)

- R12 1MΩ (brown, black, black, yellow)

- U10 socket MAX822CPA

- J10

- R13, R14 (optional)

R13 and R14 are used to set the trip-point of the low-battery indicator. These components are not included in the kit. See subsection 3.4 for more information.

## 1.3.2 SMD LDO Assembly

Solder the top side components:

- U11 TPS780330220DDC

- C11, C12

- J10

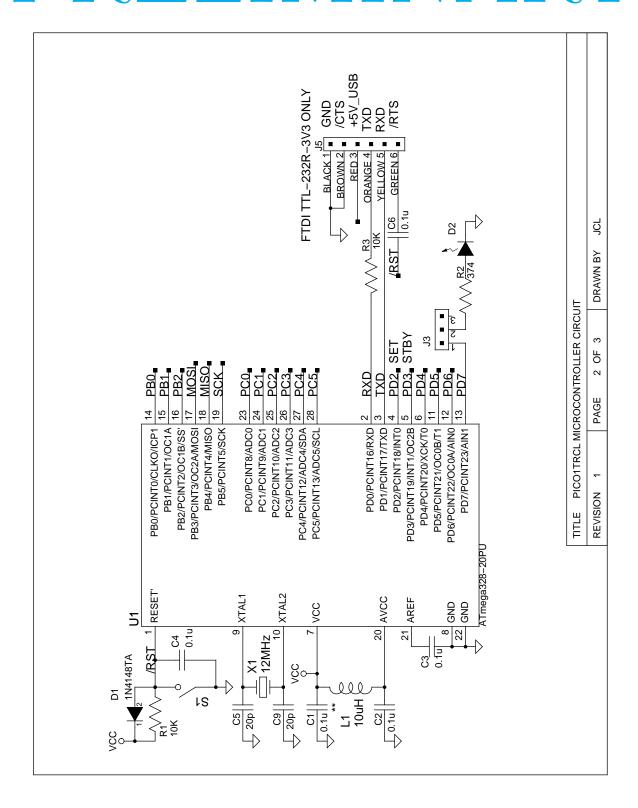

## 1.4 Microcontroller Circuit Assembly

Solder the top side components:

• C1, C2, C3, C13, C4 (optional).

C4 is optional and is not included in the kit. It is meant for applications that require additional filtering of the reset line. The reset function that uses the /RTS line from the USB interface will not function with C4 installed.

• D2

The negative lead of the LED is the short lead. Align the short lead with the negative marking on the PCB.

• R2

For 3.3V operation use the 374 $\Omega$  (orange, violet, yellow, black, brown). For 5V operation use the 1K $\Omega$  (brown, black, black brown, brown)

$10 \text{K}\Omega$  (brown, black, black, red, brown)

- J3

- J5

- X1, C5, C9

- U1 (socket)

### 1.5 Electro-mechanical Components

Since the reset switch (S1) is sensitive to washing it should be placed on last. Lightly clean the board after the switch is installed. If water does get into the switch let it dry out before applying power.

Solder the top side components:

• S1

### IC Installation and Test 1.6

### 1.6.1 U23 (DS1337)

Remove the DS1337 from the antistatic foam and insert it into the socket aligning the notch in the IC package with the notch mark indicated on the PCB silkscreen. Be careful to align pins on both sides of the socket prior to pressing the IC into the socket.

### 1.6.2U1 (ATmega328P)

Remove the ATmega328P from the antistatic foam and insert it into the socket aligning the notch in the IC package with the notch mark indicated on the PCB silkscreen. Be careful to align pins on both sides of the socket prior to pressing the IC into the socket.

## 1.6.3 B21 (CR1220 coin cell)

Install a CR1220 coin cell into the battery holder (B21) observing the polarity indicated on the holder.

The PICO1TRCL should now be fully functional and is ready to program (see section 5). Depending on the application some of the pins on the U1 socket should be removed (see subsection 1.7).

## Pin Removal

After operation of the PICO1TRCL is verified it is recommended that some of the U1 pins be cut flush to the PCB level. Each application is different and needs to reviewed. Pins like XTAL1 and XTAL2 can be affected by stray capacitance and noise. For most applications cutting the XTAL1, XTAL2, AREF and AVCC is recommended.

If your application may change over time then leave all pins intact and use care in your layout.

The XTAL circuit is susceptible to stray capacitance and noise so pins 9 and 10 should be cut flush to the PCB.

### 1.7.2**AREF**

If you are not using an external analog reference then cut pin 21 flush to the board.

## 1.7.3 AVCC

If you are not powering the ADC from a different source then pin 20 should be cut flush to the board.

### $\mathbf{2}$ IO Connectors

J5 USB header for an FTDI TTL-232R-3V3 cable.

J10 Input power header. See subsection 3.1

### 3 Electrical Hints

### Power Supply 3.1

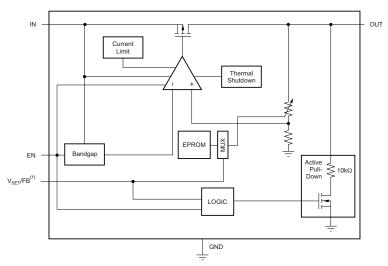

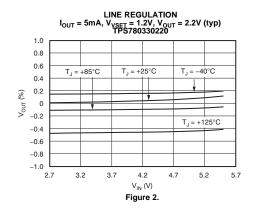

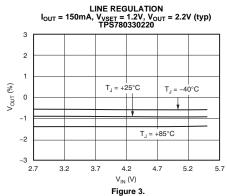

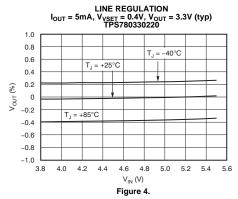

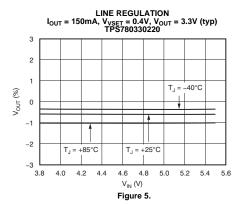

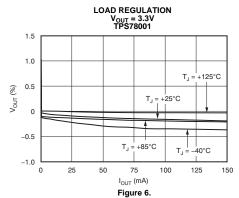

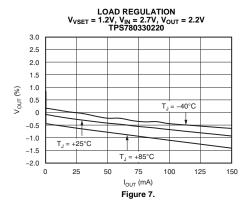

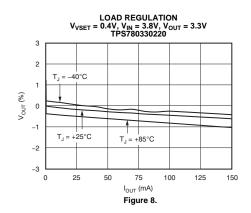

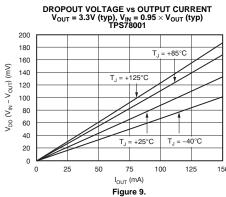

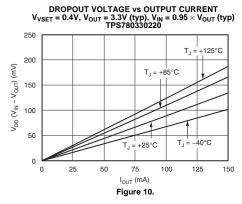

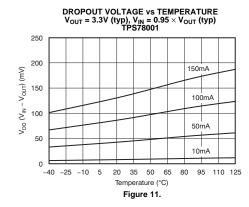

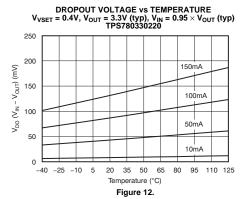

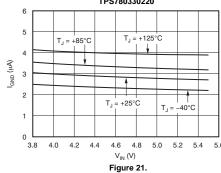

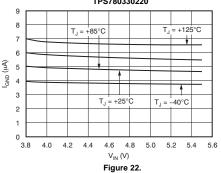

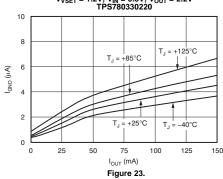

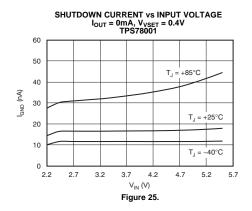

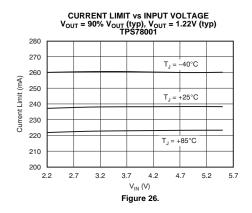

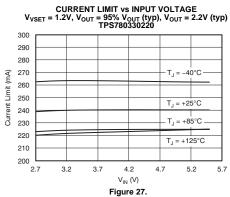

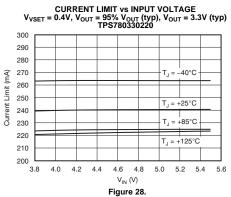

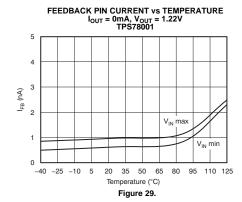

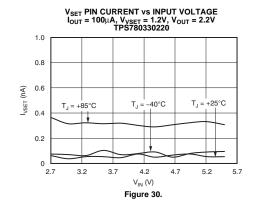

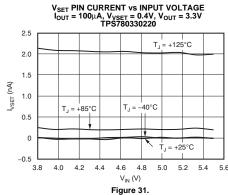

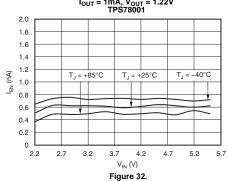

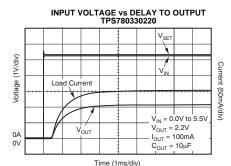

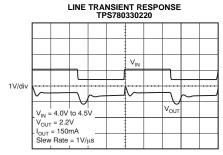

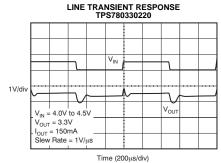

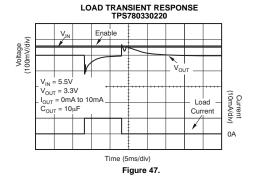

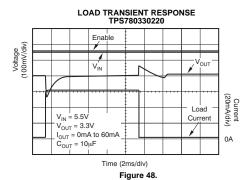

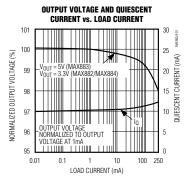

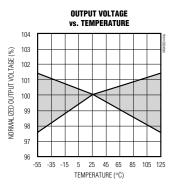

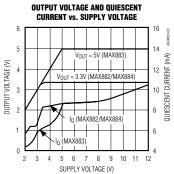

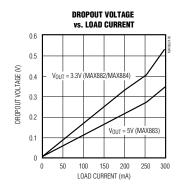

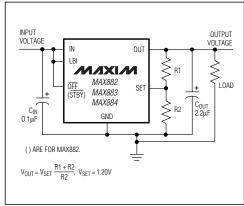

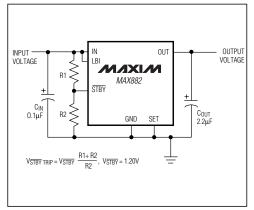

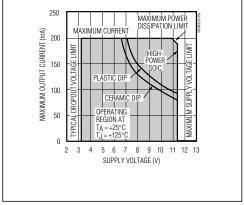

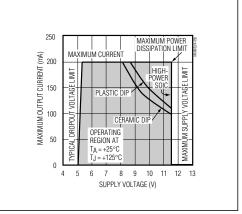

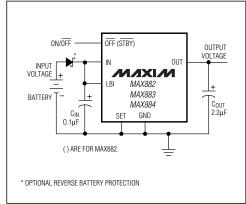

The PICO1TRCL is powered by a DC input source connected to J10. It is recommended that the PICO1TRCL be operated from a 5V supply. The SMD LDO (TPS780330220DDC) kit can be operated up to 5.5V. The TH LDO (MAX882CPA) can be operated up to 11.5V but care needs to be taken so that the maximum junction temperature  $(T_{jmax})$  of the LDO is not exceeded.

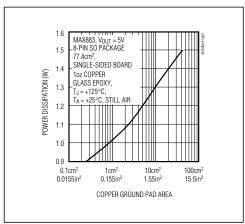

### 3.1.1Calculating LDO Junction Temperature

The power dissipation in the LDO (SMD or TH) is

$$P_{diss} = V_{drop} \cdot I_{out}$$

where

$$V_{drop} = V_{in} - V_{out}$$

$V_{in}$  is the input voltage to the PICO1TRCL

$V_{out}$  is the output voltage of the LDO

$I_{out}$  is the current out of the LDO

The junction temperature of the LDO is

$$T_J = P_{DISS} \cdot R_{\theta JA} + T_{AMBIENT}$$

where

$R_{\theta JA}$  is the thermal resistance of the LDO. The SMD LDO (TPS780330220DDC) has 200°C/W for the SMD LDO (TPS780330220DDC) and 110°C/W for the TH LDO (MAX882CPA).

$T_{AMBIENT}$  is the ambient temperature that the PICO1TRCL is operating at.

For the SMD kit the maximum junction temperature  $(T_{JMAX})$  of the LDO is 125°C, for the TH kit the  $T_{JMAX}$  is 150°C.

Table 1:  $T_{JMAX}$  for the PICO1TRCL LDO

## 3.2 Changing $V_{cc}$ using Software

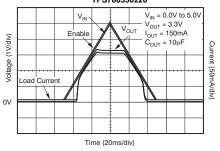

The LDO on the PICO1TRCL can be changed digitally by the ATmega328P. When the LDO SET pin is set to a logic zero the LDO output is set to 3.3V. When the SET pin is at logic one the output goes to 2.2V. This is useful for reducing power consumption when the ATmega328P is in sleep mode.

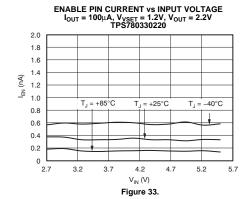

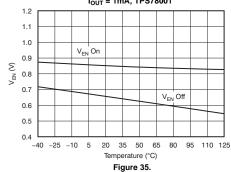

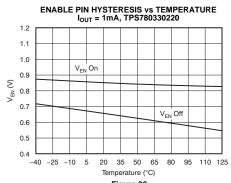

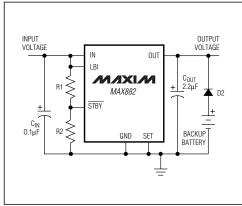

## 3.3 Enable/Standby Pins

The TH LDO (MAX882CPA) and SMD LDO (TPS780330220DDC) have enable pins. On the TH LDO (MAX882CPA) the enable pin is labeled STBY. On the SMD LDO (TPS780330220DDC) it is EN. The net on the schematic is labeled STBY. A low value disables the LDO, a high value enables it.

Since most applications will never disable the LDO it is recommended that R15 be replaced with a jumper wire, R16 be left open and jumper J12 be cut to free up the AT-mega328P line connected to STBY (EN on the SMDLDO). These changes will be made to the next revision of the board.

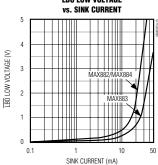

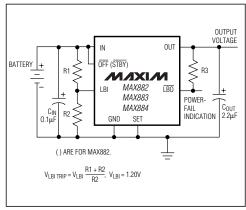

## 3.4 Low-Battery Indicator (TH-KIT ONLY)

The TH LDO (MAX882CPA) has a low-battery output (LBO) which is an open-drain output that goes low when the LBI pin is less the 1.2V. The R13, R14 divider sets the low-battery trip point. The LBI trip point level is –

$$V_{LBITRIP} = 1.2 \text{V} \cdot \frac{R_{13} + R_{14}}{R_{14}}$$

If the low-battery indicator is not required short R13 with a jumper wire and leave R14 open.

The LBO is connected to testpoint 11 (TP11). Wire TP11 to any unused ATmega328P I/O line. Since the LBO is an open-drain line it is necessary to use the ATmega328P internal pull-up resistors.

## 4 Real-Time Clock

The PICO1TRCL real-time clock (RTC) consists of a DS1337 that is powered by a CR1220 coin cell or the

PICOITRCL linear regulator (U10). The or ing diodes, D21 and D22, will output the higher voltage to the RTC (U23).

Communication to the DS1337 is through the  $I^2C$  interface (a.k.a. two-wire or TWI). The  $I^2C$  pullup resistors are on board (10K $\Omega$ ). The interrupt lines, /INTA and /INTB are jumpered to PC3 (Arduino pin 17) and PC0 (Arduino pin 14) respectively. There are no pullup resistors on the interrupt lines. If external pullups are not added then the internal pullups of the ATmega328P need to be used.

Programming the RTC requires a software library for the DS1337 and for the TWI interface. Both of these libraries are on the wiblocks site.

## 4.1 I<sup>2</sup>C Pullup Resistors

The maximum bus capacitance of the I<sup>2</sup>C bus is 400pF. Unless a large number of devices are on the bus or devices are connected using long cables PICO1TRCL system will not get close to this limit. The DS1337 represents a maximum load of 10pF.

The minimum pullup resistance is 966 $\Omega$  ( $\frac{V_{CC}-0.4V}{3mA}$ ). The maximum value pullup resistance is

$$R_{pullup(max)} = \begin{cases} \frac{1000 \text{nS}}{C_{BUS}} & \text{if } F_{SCL} \leq 100 \text{kHz}, \\ \\ \frac{300 \text{nS}}{C_{BUS}} & \text{if } 100 \text{kHz} < F_{SCL} \leq 400 \text{kHz}. \end{cases}$$

where  $C_{BUS}$  is the maximum bus capacitance, , and  $V_{CC}$  is 3.3V for the PICO1TRCL.

With a 100pF load (10 times the DS1337 load), the maximum resistance for 400kHz operation is  $3K\Omega$ . For 100kHz the maximum resistance is  $10K\Omega$ . If only the DS1337 is on the I<sup>2</sup>C bus the maximum resistances would be  $100K\Omega$  (100kHz) and  $30K\Omega$  (400kHz). The minimum resistance, which is not dependent on bus capacitance, is  $966\Omega$  for any operating frequency and  $C_{BUS}$ . (Atmel, 2009a)

| CBUS               | 100                             | рF                            | <b>400</b> pF                   |                           |  |

|--------------------|---------------------------------|-------------------------------|---------------------------------|---------------------------|--|

| Frequency          | Resistance<br>Min Max           |                               | Resistance<br>Min Max           |                           |  |

| <b>100</b> kHz     | $\frac{1150\Omega}{1150\Omega}$ | $\frac{10K\Omega}{10K\Omega}$ | $\frac{1150\Omega}{1150\Omega}$ | $\frac{1000}{2500\Omega}$ |  |

| $400 \mathrm{kHz}$ | $1150\Omega$                    | $3\mathrm{K}\Omega$           | -Not Pr                         | actical-                  |  |

Table 2: I<sup>2</sup>C Pullup Resistors

## 4.2 DS1337 Interrupt Lines

The DS1337 interrupt lines, /INTA and /INTB are jumpered to PC3 (Arduino pin 17) and PC0 (Arduino pin 14) respectively. To disconnect /INTA cut jumper J24. To disconnect /INTB cut jumper J27.

There are no pullup resistors connected to the interrupt lines. To use the interrupt lines with the ATmega328P the internal pull-up resistors need to be enabled. For the ATmega328P  $20K\Omega \leq R_{pullup} \leq 50K\Omega$  which is sufficient to pullup the DS1337 lines. (Atmel, 2009b).

## 4.3 RTC Battery Life

The DS1337 operates with a  $V_{CC}$  from 1.8V to 5.5V. When power is removed from the PICO1TRCL the DS1337 is in standby mode and the maximum standby current is  $1.5\mu A(Maxim, 2009a)$ . The CR1220 coin cell has a capacity of 40mAH (to 2V). The battery life is  $\approx 26000$  hours.

## 4.4 Prototype Area

To the right of the RTC there is a small prototype area. Eight test points are provided to connect circuitry from the prototype area to the ATmega328P. With the PICO1TRCL rotated 90 degrees clockwise there is a row of six pins at the top and two pins at the bottom. The pinout is shown in Table 3.

| Pin       | Arduino           | Notes        |

|-----------|-------------------|--------------|

| Name      | $\mathbf{Number}$ |              |

| GND       |                   | left top     |

| SDA (PC4) | A4                |              |

| SCL (PC5) | A5                |              |

| PB1       | 9                 |              |

| PB2       | 10                |              |

| VCC       |                   | right top    |

| GND       |                   | left bottom  |

| VCC       |                   | right bottom |

Table 3: Prototype Area Pins

## 4.5 Debug LED

The debug LED, D2, can be connected to U1 pin 13 (PD7) of the ATmega328P or left disconnected. U1 pin 13 corresponds to Arduino pin 7

LED jumper in the disconnected position

LED jumper in the PD7 position

## 4.6 Pinout

The input and output pins for the PICO1TRCL are the socket pins of the microcontroller (U1). The pinout is listed in Table 4.

| Pin               | Pin   | Arduino           | Notes                |

|-------------------|-------|-------------------|----------------------|

| $\mathbf{Number}$ | Name  | $\mathbf{Number}$ |                      |

| 2                 | RXD   | 0                 |                      |

| 3                 | TXD   | 1                 |                      |

| 4                 | PD2   | 2                 |                      |

| 5                 | PD3   | 3                 |                      |

| 6                 | PD4   | 4                 |                      |

| 11                | PD5   | 5                 |                      |

| 12                | PD6   | 6                 |                      |

| 13                | PD7   | 7                 | Debug LED            |

| 14                | PB0   | 8                 |                      |

| 15                | PB1   | 9                 |                      |

| 16                | PB2   | 10                |                      |

| 17                | PB3   | 11                | MOSI                 |

| 18                | PB4   | 12                | MISO                 |

| 19                | PB5   | 13                | SCK                  |

| 23                | PC0   | A0                |                      |

| 24                | PC1   | A1                |                      |

| 25                | PC2   | A2                |                      |

| 26                | PC3   | A3                |                      |

| 27                | PC4   | A4                | SDA                  |

| 28                | PC5   | A5                | $\operatorname{SCL}$ |

| 1                 | Reset |                   |                      |

| 9                 | XTAL1 |                   | PB6                  |

| 10                | XTAL2 |                   | PB7                  |

| 7                 | VCC   |                   |                      |

| 20                | AVCC  |                   |                      |

| 21                | AREF  |                   |                      |

| 8                 | GND   |                   |                      |

| 22                | GND   |                   |                      |

|                   |       |                   |                      |

Table 4: U1 Pinout

## 5 Programming the PICO1TRCL

The PICO1TRCL can be programmed using the Arduino tools (version 0012 or later). Connect an FTDI TTL-232R-3V3 cable to header J5 with the black wire aligned to pin one.

## 5.1 Selecting the proper board

In order for the Arduino tools to recognize the wiblocks boards additional lines need to be added to the boards.txt file. The additional lines are shown in Listing 1 (with annotations). A file containing these adddions can be downloaded from wiblocks. Once boards.txt is modified select wiblocks 328 at 12MHz from the Tools->Board menu.

## 5.2 Downloading a program

The PICO1TRCL must be rebooted to start the program download. This can be done by pressing the reset button S1 immediately before starting the download. If your USB port is configured to set RTS on close then the reset will occur automatically.

Listing 1: boards.txt Modifications for the PICO1TRCL

- uiblocks\_328.name=wiblocks 328 at 12MHz

- <sup>2</sup> wiblocks\_328. upload.protocol=stk500

- $_3$  wiblocks\_328.upload.maximum\_size=30720

- $_4$  wiblocks\_328.**upload**.**speed**=19200

- 5 wiblocks\_328.bootloader.low\_fuses=0xff

- $_{6}$  wiblocks\_328.bootloader.high\_fuses=0xdd

- $_{7}$  wiblocks\_328.bootloader.extended\_fuses=0x00

- s wiblocks\_328.bootloader.path=atmega328

- 9 wiblocks\_328.bootloader.file=wiblocks\_328.hex

- unlocks\_328.**bootloader**.unlock\_bits=0x3F

- $^{11}$  wiblocks\_328.bootloader.lock\_bits=0x0F

- wiblocks\_328. build.mcu=atmega328p

- $^{13}$  wiblocks\_328. **build**. **f\_cpu**=12000000L

- $_{14}$  wiblocks\_328. build.core=arduino

Atmel. (2009a). 8-bit AVR Microcontroller with 4/8/16/32K Bytes In-System Programmable Flash., 323. (Retrieved March 14, 2009, from http://www.atmel.com/dyn/resources/prod\_documents/doc8025.pdf)

Atmel. (2009b). 8-bit AVR Microcontroller with 4/8/16/32K Bytes In-System Programmable Flash., 314. (Retrieved March 14, 2009, from http://www.atmel.com/dyn/resources/prod\_documents/doc8025.pdf)

Atmel. (2009c). 8-bit AVR Microcontroller with 4/8/16/32K Bytes In-System Programmable Flash.

(Retrieved March 14, 2009, from http://www.atmel.com/dyn/resources/prod\_documents/doc8025.pdf)

Maxim. (2009a, July). DS1337 I2C Serial Real-Time Clock., 2-3. (Retrieved September 30, 2009, from http://datasheets.maxim-ic.com/en/ds/DS1337-DS1337C.pdf)

Maxim. (2009b, July). DS1337 I2C Serial Real-Time Clock.

(Retrieved September 30, 2009, from http://datasheets.maxim-ic.com/en/ds/DS1337-DS1337C.pdf)

## 6 Assembly Documentation and Schematics

Table 5: Bill of Materials

Kit: PICO1TRCL-SMD-KIT

| Qty | Reference       | Part Number                  | Description                                   |

|-----|-----------------|------------------------------|-----------------------------------------------|

| 1   | B21             | CON_BATKeystone_500          | connector, battery, CR1220                    |

| 5   | C1, C2, C3, C6, | CAPR-0U10-50V-X7R-100M       | capacitor, ceramic, 0.1uF, 10%, 50V, X7R      |

|     | C23             |                              |                                               |

| 2   | C5, C9          | CAPR-20P0-100V-NPO-5T00      | capacitor, ceramic, 20pF                      |

| 2   | C11, C12        | CAPR-2U20-10V-X5R-5MM        | capacitor, ceramic, 2.2uF, 10%, 10V, X5R      |

| 1   | D1              | DIOA-1N4148                  | diode, 1N4148                                 |

| 1   | D2              | LEDR-1T-GRN-2M00             | LED, T1, Green                                |

| 2   | D21, D22        | DIOA-BAT41                   | diode, BAT41                                  |

| 1   | J3              | $HDR_BR-3X1-100M$            | header, 3x1, 100mils                          |

| 1   | J5              | $HDR_BR-6X1-100M$            | header, 6x1, 100mils                          |

| 1   | J10             | $HDR_BR-2X1-100M$            | header, 2x1, 100mils                          |

| 1   | L1              | INDA-10UH-130M-10T0          | inductor, $10uH$ , $10\%$                     |

| 4   | R1, R3, R22,    | RES-10K0-0W125-1T00          | resistor, 10K, 1/8W, 1%                       |

|     | R23             |                              |                                               |

| 1   | R2              | RES-374R-0W125-1T00          | resistor, 374 Ohm, 1/8W, 1%                   |

| 1   | S1              | SW_Panasonic_EVQ-PAE04M      | pushbutton                                    |

| 1   | U1              | $IC\_ATMEL\_ATmega328-20PU$  | ATmega328-20PU, 32K/1K/2K, 20MHz              |

| 1   | U11             | $TI_TPS780330220DDC$         |                                               |

| 1   | U23             | $IC\_RTC\_\_Maxim\_DS1337 +$ | IC, RTC, DS1337+                              |

| 1   | X1              | XTAL-12M-20P-HC49US          | crystal, 12MHz, 20pF, HC49US                  |

| 1   | X21             | XTAL-32K768-6P-2X6           | crystal, 32.768KHz, 6pF, 2x6mm package        |

| 1   |                 | DIP-8P-300M                  | DIP Socket, 8 Pin, 300mil centers             |

| 1   |                 | $JMP\_Adamtech\_MSBHG$       | Shunt with handle                             |

| 1   |                 | $DIP_WW-28P-300M$            | DIP Socket, 28 Pin, 300mil centers, Wire Wrap |

| 1   |                 | $wiblock\_PICO1TRCL-PCB$     |                                               |

## wiblock® PICO1TRCL Table 6: Component List

Kit: PICO1TRCL-SMD-KIT

| Reference | Part Number                 | Description                                   |

|-----------|-----------------------------|-----------------------------------------------|

| B21       | CON_BATKeystone_500         | connector, battery, CR1220                    |

| C1        | CAPR-0U10-50V-X7R-100M      | capacitor, ceramic, 0.1uF, 10%, 50V, X7R      |

| C2        | CAPR-0U10-50V-X7R-100M      | capacitor, ceramic, 0.1uF, 10%, 50V, X7R      |

| C3        | CAPR-0U10-50V-X7R-100M      | capacitor, ceramic, 0.1uF, 10%, 50V, X7R      |

| C6        | CAPR-0U10-50V-X7R-100M      | capacitor, ceramic, 0.1uF, 10%, 50V, X7R      |

| C23       | CAPR-0U10-50V-X7R-100M      | capacitor, ceramic, 0.1uF, 10%, 50V, X7R      |

| C5        | CAPR-20P0-100V-NPO-5T00     | capacitor, ceramic, 20pF                      |

| C9        | CAPR-20P0-100V-NPO-5T00     | capacitor, ceramic, 20pF                      |

| C11       | CAPR-2U20-10V-X5R-5MM       | capacitor, ceramic, 2.2uF, 10%, 10V, X5R      |

| C12       | CAPR-2U20-10V-X5R-5MM       | capacitor, ceramic, 2.2uF, 10%, 10V, X5R      |

| D1        | DIOA-1N4148                 | diode, 1N4148                                 |

| D2        | LEDR-1T-GRN-2M00            | LED, T1, Green                                |

| D21       | DIOA-BAT41                  | diode, BAT41                                  |

| D22       | DIOA-BAT41                  | diode, BAT41                                  |

| J3        | $HDR_BR-3X1-100M$           | header, 3x1, 100mils                          |

| J5        | $HDR_BR-6X1-100M$           | header, 6x1, 100mils                          |

| J10       | $HDR_BR-2X1-100M$           | header, 2x1, 100mils                          |

| L1        | INDA-10UH-130M-10T0         | inductor, $10uH$ , $10\%$                     |

| R1        | RES-10K0-0W125-1T00         | resistor, 10K, 1/8W, 1%                       |

| R3        | RES-10K0-0W125-1T00         | resistor, 10K, 1/8W, 1%                       |

| R22       | RES-10K0-0W125-1T00         | resistor, 10K, 1/8W, 1%                       |

| R23       | RES-10K0-0W125-1T00         | resistor, 10K, 1/8W, 1%                       |

| R2        | RES-374R-0W125-1T00         | resistor, 374 Ohm, 1/8W, 1%                   |

| S1        | $SW\_Panasonic\_EVQ-PAE04M$ | pushbutton                                    |

| U1        | $IC\_ATMEL\_ATmega328-20PU$ | ATmega328-20PU, 32K/1K/2K, 20MHz              |

| U11       | $TI_TPS780330220DDC$        |                                               |

| U23       | $IC_RTC_Maxim_DS1337+$      | IC, RTC, DS1337+                              |

| X1        | XTAL-12M-20P-HC49US         | crystal, 12MHz, 20pF, HC49US                  |

| X21       | XTAL-32K768-6P-2X6          | crystal, 32.768KHz, 6pF, 2x6mm package        |

|           | DIP-8P-300M                 | DIP Socket, 8 Pin, 300mil centers             |

|           | $JMP\_Adamtech\_MSBHG$      | Shunt with handle                             |

|           | $DIP_WW-28P-300M$           | DIP Socket, 28 Pin, 300mil centers, Wire Wrap |

|           | $wiblock\_PICO1TRCL-PCB$    |                                               |

**Kit:** PICO1TRCL-TH-KIT

| Qty | Reference       | Part Number                                                            | Description                                   |

|-----|-----------------|------------------------------------------------------------------------|-----------------------------------------------|

| 1   | B21             | CON_BATKeystone_500                                                    | connector, battery, CR1220                    |

| 6   | C1, C2, C3, C6, | CAPR-0U10-50V-X7R-100M                                                 | capacitor, ceramic, 0.1uF, 10%, 50V, X7R      |

|     | C13, C23        |                                                                        |                                               |

| 2   | C5, C9          | CAPR-20P0-100V-NPO-5T00                                                | capacitor, ceramic, 20pF                      |

| 2   | C11, C12        | CAPR-2U20-10V-X5R-5MM                                                  | capacitor, ceramic, 2.2uF, 10%, 10V, X5R      |

| 1   | D1              | DIOA-1N4148                                                            | diode, 1N4148                                 |

| 1   | D2              | LEDR-1T-GRN-2M00                                                       | LED, T1, Green                                |

| 2   | D21, D22        | DIOA-BAT41                                                             | diode, BAT41                                  |

| 1   | J3              | $HDR_BR-3X1-100M$                                                      | header, 3x1, 100mils                          |

| 1   | J5              | $HDR_BR-6X1-100M$                                                      | header, 6x1, 100mils                          |

| 1   | J10             | $HDR_BR-2X1-100M$                                                      | header, 2x1, 100mils                          |

| 1   | L1              | INDA-10UH-130M-10T0                                                    | inductor, 10uH, 10%                           |

| 4   | R1, R3, R22,    | RES-10K0-0W125-1T00                                                    | resistor, 10K, 1/8W, 1%                       |

|     | R23             |                                                                        |                                               |

| 1   | R2              | RES-374R-0W125-1T00                                                    | resistor, 374 Ohm, 1/8W, 1%                   |

| 1   | R11             | RES-845K-0W125-1T00                                                    | resistor, 845K, 1/8W, 1%                      |

| 1   | R12             | RES-1M00-0W125-1T00                                                    | resistor, $1.0M$ , $1/8W$ , $1\%$             |

| 1   | S1              | SW_Panasonic_EVQ-PAE04M                                                | pushbutton                                    |

| 1   | U1              | $IC\_ATMEL\_ATmega328-20PU$                                            | ATmega328-20PU, 32K/1K/2K, 20MHz              |

| 1   | U10             | $Maxim\_MAX882CPA$                                                     |                                               |

| 1   | U23             | $IC\_RTC\_\_Maxim\_DS1337 +$                                           | IC, RTC, DS1337+                              |

| 1   | X1              | XTAL-12M-20P-HC49US                                                    | crystal, 12MHz, 20pF, HC49US                  |

| 1   | X21             | XTAL-32K768-6P-2X6                                                     | crystal, 32.768KHz, 6pF, 2x6mm package        |

| 2   |                 | DIP-8P-300M                                                            | DIP Socket, 8 Pin, 300mil centers             |

| 1   |                 | $JMP\_Adamtech\_MSBHG$                                                 | Shunt with handle                             |

| 1   |                 | $\mathrm{DIP}_{-}\mathrm{WW}\text{-}28\mathrm{P}\text{-}300\mathrm{M}$ | DIP Socket, 28 Pin, 300mil centers, Wire Wrap |

| 1   |                 | wiblock_PICO1TRCL-PCB                                                  |                                               |

Kit: PICO1TRCL-TH-KIT

| Reference | Part Number                                                            | Description                                   |

|-----------|------------------------------------------------------------------------|-----------------------------------------------|

| B21       | CON_BATKeystone_500                                                    | connector, battery, CR1220                    |

| C1        | CAPR-0U10-50V-X7R-100M                                                 | capacitor, ceramic, 0.1uF, 10%, 50V, X7R      |

| C2        | CAPR-0U10-50V-X7R-100M                                                 | capacitor, ceramic, 0.1uF, 10%, 50V, X7R      |

| C3        | CAPR-0U10-50V-X7R-100M                                                 | capacitor, ceramic, 0.1uF, 10%, 50V, X7R      |

| C6        | CAPR-0U10-50V-X7R-100M                                                 | capacitor, ceramic, 0.1uF, 10%, 50V, X7R      |

| C13       | CAPR-0U10-50V-X7R-100M                                                 | capacitor, ceramic, 0.1uF, 10%, 50V, X7R      |

| C23       | CAPR-0U10-50V-X7R-100M                                                 | capacitor, ceramic, 0.1uF, 10%, 50V, X7R      |

| C5        | CAPR-20P0-100V-NPO-5T00                                                | capacitor, ceramic, 20pF                      |

| C9        | CAPR-20P0-100V-NPO-5T00                                                | capacitor, ceramic, 20pF                      |

| C11       | CAPR-2U20-10V-X5R-5MM                                                  | capacitor, ceramic, 2.2uF, 10%, 10V, X5R      |

| C12       | CAPR-2U20-10V-X5R-5MM                                                  | capacitor, ceramic, 2.2uF, 10%, 10V, X5R      |

| D1        | DIOA-1N4148                                                            | diode, 1N4148                                 |

| D2        | LEDR-1T-GRN-2M00                                                       | LED, T1, Green                                |

| D21       | DIOA-BAT41                                                             | diode, BAT41                                  |

| D22       | DIOA-BAT41                                                             | diode, BAT41                                  |

| J3        | $HDR_BR-3X1-100M$                                                      | header, 3x1, 100mils                          |

| J5        | $HDR_BR-6X1-100M$                                                      | header, 6x1, 100mils                          |

| J10       | $HDR_BR-2X1-100M$                                                      | header, 2x1, 100mils                          |

| L1        | INDA-10UH-130M-10T0                                                    | inductor, 10uH, 10%                           |

| R1        | RES-10K0-0W125-1T00                                                    | resistor, 10K, 1/8W, 1%                       |

| R3        | RES-10K0-0W125-1T00                                                    | resistor, 10K, 1/8W, 1%                       |

| R22       | RES-10K0-0W125-1T00                                                    | resistor, 10K, 1/8W, 1%                       |

| R23       | RES-10K0-0W125-1T00                                                    | resistor, 10K, 1/8W, 1%                       |

| R2        | RES-374R-0W125-1T00                                                    | resistor, 374 Ohm, 1/8W, 1%                   |

| R11       | RES-845K-0W125-1T00                                                    | resistor, 845K, 1/8W, 1%                      |

| R12       | RES-1M00-0W125-1T00                                                    | resistor, 1.0M, 1/8W, 1%                      |

| S1        | $SW\_Panasonic\_EVQ-PAE04M$                                            | pushbutton                                    |

| U1        | IC_ATMEL_ATmega328-20PU                                                | ATmega328-20PU, 32K/1K/2K, 20MHz              |

| U10       | Maxim_MAX882CPA                                                        |                                               |

| U23       | $IC_RTC_Maxim_DS1337+$                                                 | IC, RTC, DS1337+                              |

| X1        | XTAL-12M-20P-HC49US                                                    | crystal, 12MHz, 20pF, HC49US                  |

| X21       | XTAL-32K768-6P-2X6                                                     | crystal, 32.768KHz, 6pF, 2x6mm package        |

|           | DIP-8P-300M                                                            | DIP Socket, 8 Pin, 300mil centers             |

|           | $JMP\_Adamtech\_MSBHG$                                                 | Shunt with handle                             |

|           | $\mathrm{DIP}_{-}\mathrm{WW}\text{-}28\mathrm{P}\text{-}300\mathrm{M}$ | DIP Socket, 28 Pin, 300mil centers, Wire Wrap |

|           | wiblock_PICO1TRCL-PCB                                                  |                                               |

Figure 1: PICO1TRCL Top Side Assembly Drawing (Rev 1)

Figure 2: PICO1TRCL Bottom Side Assembly Drawing (Rev 1)

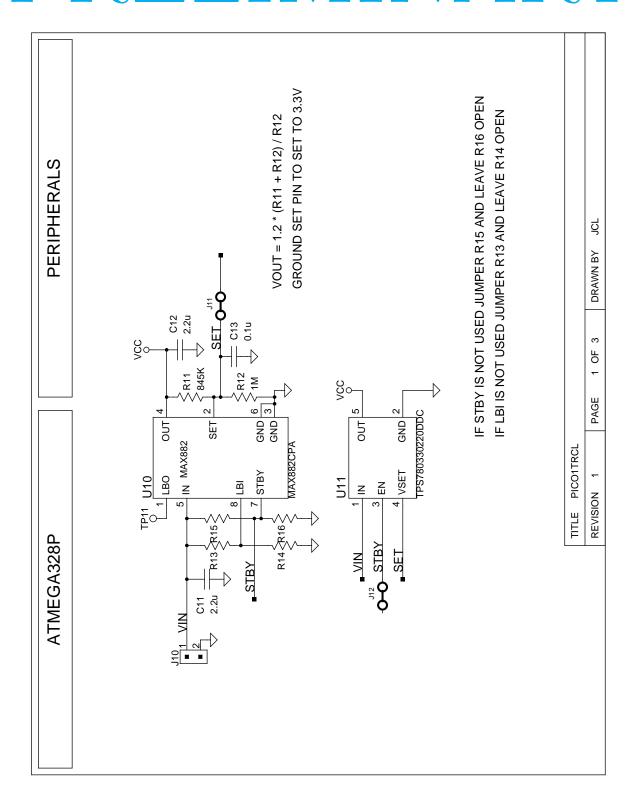

Figure 3: PICO1TRCL (Rev 1)

Figure 4: PICO1TRCL (Rev 1)

Figure 5: PICO1TRCL (Rev 1)

19-4652; 7/09

## DS1337 I<sup>2</sup>C Serial Real-Time Clock

## www.maxim-ic.com

## **GENERAL DESCRIPTION**

The DS1337 serial real-time clock is a low-power clock/calendar with two programmable time-of-day alarms and a programmable square-wave output. Address and data are transferred serially through an  $\rm l^2C$  bus. The clock/calendar provides seconds, minutes, hours, day, date, month, and year information. The date at the end of the month is automatically adjusted for months with fewer than 31 days, including corrections for leap year. The clock operates in either the 24-hour or 12-hour format with AM/PM indicator.

The device is fully accessible through the serial interface while  $V_{\text{CC}}$  is between 1.8V and 5.5V.  $I^2C$  operation is not guaranteed below 1.8V. Timekeeping operation is maintained with  $V_{\text{CC}}$  as low as 1.3V

## **APPLICATIONS**

Handhelds (GPS, POS Terminal, MP3 Player)

Consumer Electronics (Set-Top Box, VCR/Digital Recording)

Office Equipment (Fax/Printer, Copier)

Medical (Glucometer, Medicine Dispenser)

Telecommunications (Router, Switch, Server)

Other (Utility Meter, Vending Machine, Thermostat, Modem)

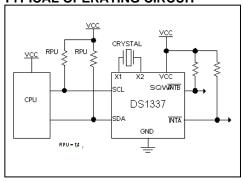

## TYPICAL OPERATING CIRCUIT

## **FEATURES**

- Real-Time Clock (RTC) Counts Seconds, Minutes, Hours, Day, Date, Month, and Year with Leap-Year Compensation Valid Up to 2100

- Available in a Surface-Mount Package with an Integrated Crystal (DS1337C)

- I<sup>2</sup>C Serial Interface

- Two Time-of-Day Alarms

- Oscillator Stop Flag

- Programmable Square-Wave Output Defaults to 32kHz on Power-Up

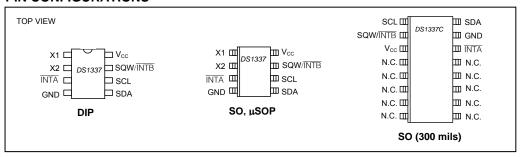

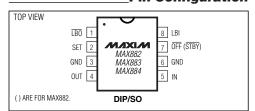

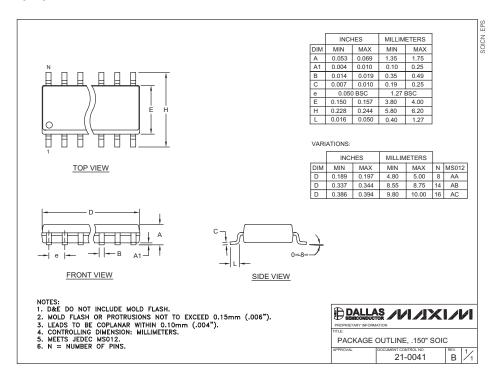

- Available in 8-Pin DIP, SO, or µSOP

- -40°C to +85°C Operating Temperature Range

## **ORDERING INFORMATION**

| PART     | TEMP RANGE     | PIN-PACKAGE      | TOP<br>MARK† |

|----------|----------------|------------------|--------------|

| DS1337+  | -40°C to +85°C | 8 DIP (300 mils) | DS1337       |

| DS1337S+ | -40°C to +85°C | 8 SO (150 mils)  | DS1337       |

| DS1337U+ | -40°C to +85°C | 8 μSOP           | 1337         |

| DS1337C# | -40°C to +85°C | 16 SO (300 mils) | DS1337C      |

- + Denotes a lead(Pb)-free/RoHS-compliant device.

- # Denotes a RoHS-compliant device that may include lead that is exempt under the RoHS requirements. The lead finish is JESD97 category e3, and is compatible with both lead-based and lead-free soldering processes.

- † A "+" anywhere on the top mark denotes a lead-free device. A "#" denotes a RoHS-compliant device.

Pin Configurations appear at end of data sheet.

**Note:** Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device may be simultaneously available through various sales channels. For information about device errata, go to: <a href="https://www.maxim-ic.com/errata">www.maxim-ic.com/errata</a>.

DS1337 I<sup>2</sup>C Serial Real-Time Clock

## **ABSOLUTE MAXIMUM RATINGS**

| Voltage Range on Any Pin Relative to Ground | 0.3V to +6.0V |

|---------------------------------------------|---------------|

| Operating Temperature Range (Noncondensing) |               |

| Storage Temperature Range                   |               |

| Soldering Temperature                       |               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to the absolute maximum rating conditions for extended periods may affect device reliability.

## RECOMMENDED DC OPERATING CONDITIONS

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C)$

| PARAMETER                      | SYMBOL           | CONDITIONS           | MIN                   | TYP | MAX                    | UNITS    |

|--------------------------------|------------------|----------------------|-----------------------|-----|------------------------|----------|

|                                | V <sub>CC</sub>  | Full operation       | 1.8                   | 3.3 | 5.5                    | ٧        |

| V <sub>CC</sub> Supply Voltage | V <sub>CCT</sub> | Timekeeping (Note 5) | 1.3                   |     | 1.8                    | <b>V</b> |

| Logic 1                        | \/               | SCL, SDA             | 0.7 x V <sub>CC</sub> |     | $V_{CC} + 0.3$         | V        |

|                                | V <sub>IH</sub>  | ĪNTĀ, SQW/ĪNTB       |                       |     | 5.5                    |          |

| Logic 0                        | V <sub>IL</sub>  |                      | -0.3                  |     | +0.3 x V <sub>CC</sub> | <b>V</b> |

## DC ELECTRICAL CHARACTERISTICS—Full Operation

$(V_{CC} = 1.8V \text{ to } 5.5V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C.}) \text{ (Note 1)}$

|                                         |                  | •            |     |     |     |       |

|-----------------------------------------|------------------|--------------|-----|-----|-----|-------|

| PARAMETER                               | SYMBOL           | CONDITIONS   | MIN | TYP | MAX | UNITS |

| Input Leakage                           | ILI              | (Note 2)     | -1  |     | +1  | μА    |

| I/O Leakage                             | I <sub>LO</sub>  | (Note 3)     | -1  |     | +1  | μА    |

| Logic 0 Output (V <sub>OL</sub> = 0.4V) | I <sub>OL</sub>  | (Note 3)     |     |     | 3   | mA    |

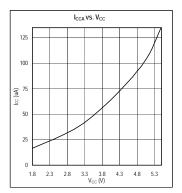

| Active Supply Current                   | I <sub>CCA</sub> | (Note 4)     |     |     | 150 | μА    |

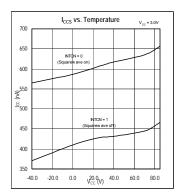

| Standby Current                         | I <sub>ccs</sub> | (Notes 5, 6) |     |     | 1.5 | μА    |

## DC ELECTRICAL CHARACTERISTICS--Timekeeping

$(V_{CC} = 1.3V \text{ to } 1.8V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C.}) \text{ (Note 1)}$

| PARAMETER                                    | SYMBOL              | CONDITIONS         | MIN | TYP | MAX | UNITS |

|----------------------------------------------|---------------------|--------------------|-----|-----|-----|-------|

| Timekeeping Current (Oscillator Enabled)     | I <sub>CCTOSC</sub> | (Notes 5, 7, 8, 9) |     | 425 | 600 | nA    |

| Data-Retention Current (Oscillator Disabled) | I <sub>CCTDDR</sub> | (Notes 5, 9)       |     |     | 100 | nA    |

DS1337 I2C Serial Real-Time Clock

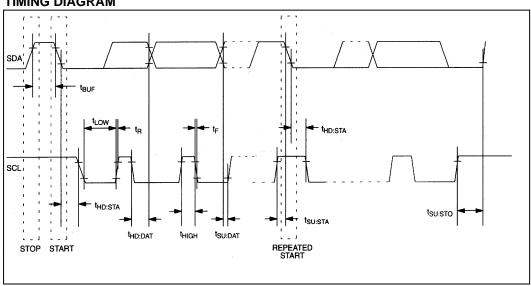

## **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC} = 1.8V \text{ to } 5.5V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C.}) \text{ (Note 1)}$

| PARAMETER                           | SYMBOL              | CONDITIONS    | MIN                    | TYP | MAX  | UNITS                                                 |  |

|-------------------------------------|---------------------|---------------|------------------------|-----|------|-------------------------------------------------------|--|

| SCI Clask Fraguency                 | ŧ                   | Fast mode     | 100                    |     | 400  | kU-                                                   |  |

| SCL Clock Frequency                 | f <sub>SCL</sub>    | Standard mode | 0                      |     | 100  | UNITS  kHz  μs  μs  μs  μs  μs  μs  μs  μs  μs  ps  p |  |

| Bus Free Time Between a             |                     | Fast mode     | 1.3                    |     |      |                                                       |  |

| STOP and START Condition            | t <sub>BUF</sub>    | Standard mode | 4.7                    |     |      | μS                                                    |  |

| Hold Time (Repeated)                |                     | Fast mode     | 0.6                    |     |      |                                                       |  |

| START Condition (Note 10)           | t <sub>HD:STA</sub> | Standard mode | 4.0                    |     |      | μς                                                    |  |

| LOW Period of SCL Clock             | t                   | Fast mode     | 1.3                    |     |      | e                                                     |  |

| LOW I GIOG OF SCE CIOCK             | t <sub>LOW</sub>    | Standard mode | 4.7                    |     |      | μδ                                                    |  |

| HIGH Period of SCL Clock            |                     | Fast mode     | 0.6                    |     |      |                                                       |  |

| HIGH Period of SCL Clock            | t <sub>HIGH</sub>   | Standard mode | 4.0                    |     |      |                                                       |  |

| Setup Time for a Repeated           |                     | Fast mode     | 0.6                    |     |      |                                                       |  |

| START Condition                     | t <sub>SU:STA</sub> | Standard mode | 4.7                    |     |      | μs<br>- μs                                            |  |

| Data Hold Time                      | 4                   | Fast mode     | 0                      |     | 0.9  |                                                       |  |

| (Notes 11, 12)                      | t <sub>HD:DAT</sub> | Standard mode | 0                      |     |      | μδ                                                    |  |

| Data Setup Time (Note 13)           | t <sub>SU:DAT</sub> | Fast mode     | 100                    |     |      | ne                                                    |  |

| . , ,                               | SU:DAT              | Standard mode | 250                    |     |      | 113                                                   |  |

| Rise Time of Both SDA and           | t <sub>R</sub>      | Fast mode     | 20 + 0.1C <sub>B</sub> |     | 300  | ne                                                    |  |

| SCL Signals (Note 14)               | чR                  | Standard mode | 20 + 0.1C <sub>B</sub> |     | 1000 | 113                                                   |  |

| Fall Time of Both SDA and           | t⊧                  | Fast mode     | $20 + 0.1C_B$          |     | 300  | ne                                                    |  |

| SCL Signals (Note 14)               | ·F                  | Standard mode | $20 + 0.1C_B$          |     | 300  | μs                   |  |

| Setup Time for STOP                 | 4                   | Fast mode     | 0.6                    |     |      |                                                       |  |

| Condition                           | t <sub>su:sto</sub> | Standard mode | 4.0                    |     |      | μs                                                    |  |

| Capacitive Load for Each Bus Line   | Св                  | (Note 14)     |                        |     | 400  | pF                                                    |  |

| I/O Capacitance (SDA, SCL)          | C <sub>I/O</sub>    | (Note 15)     |                        |     | 10   | pF                                                    |  |

| Oscillator Stop Flag (OSF)<br>Delay | t <sub>OSF</sub>    |               |                        | 100 |      | ms                                                    |  |

- Note 1: Limits at -40°C are guaranteed by design and are not production tested.

- Note 2: SCL only.

- Note 3: SDA, INTA, and SQW/INTB.

- Note 4:  $I_{CCA}$ —SCL clocking at max frequency = 400kHz,  $V_{IL}$  = 0.0V,  $V_{IH}$  =  $V_{CC}$ .

- Note 5: Specified with the  $I^2C$  bus inactive,  $V_{IL} = 0.0V$ ,  $V_{IH} = V_{CC}$ .

- Note 6: SQW enabled.

- Note 7: Specified with the SQW function disabled by setting INTCN = 1.

- Note 8: Using recommended crystal on X1 and X2.

- Note 9: The device is fully accessible when  $1.8 \le V_{\text{CC}} \le 5.5 \text{V}$ . Time and date are maintained when  $1.3 \text{V} \le V_{\text{CC}} \le 1.8 \text{V}$ .

- Note 10: After this period, the first clock pulse is generated

- Note 11: A device must internally provide a hold time of at least 300ns for the SDA signal (referred to the V<sub>IHMIN</sub> of the SCL signal) to bridge the undefined region of the falling edge of SCL.

- $\textbf{Note 12:} \qquad \text{The maximum $t_{\text{HD.DAT}}$ need only be met if the device does not stretch the LOW period $(t_{\text{LOW}})$ of the SCL signal.}$

- Note 13: A fast-mode device can be used in a standard-mode system, but the requirement t<sub>SUDAT</sub> ≥ to 250ns must then be met. This is automatically the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line t<sub>R max</sub> + t<sub>SU:DAT</sub> = 1000 + 250 = 1250ns before the SCL line is a stretch and the solution of the solution in the solution of the solution is stretched.

- lote 14: C<sub>B</sub>—total capacitance of one bus line in pF

- Note 15: Guaranteed by design. Not production tested.

## DS1337 I<sup>2</sup>C Serial Real-Time Clock

Note 16: The parameter  $t_{OSF}$  is the period of time that the oscillator must be stopped for the OSF bit to be set over the voltage range of  $V_{CC(MIN)} \le V_{CC} \le V_{CC(MAX)}$ .

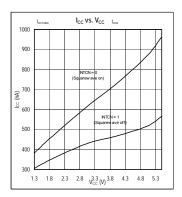

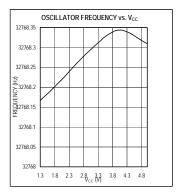

## TYPICAL OPERATING CHARACTERISTICS

( $V_{CC}$  = 3.3V,  $T_A$  = +25°C, unless otherwise noted.)

DS1337 I<sup>2</sup>C Serial Real-Time Clock

## **PIN DESCRIPTION**

| Р | PIN  |                 | FUNCTION                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|---|------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 8 | 16   | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| 1 | _    | X1              | Connections for a Standard 32.768kHz Quartz Crystal. The internal oscillator circuitry is designed for operation with a crystal having a specified load capacitance (C <sub>L</sub> ) of 6pF. For more information about crystal selection and crystal layout considerations, refer to <i>Application Note 58: Crystal</i>                           |  |  |  |  |  |  |

| 2 | _    | X2              | Considerations with Dallas Real-Time Clocks. An external 32.768kHz oscillator can also drive the DS1337. In this configuration, the X1 pin is connected to the external oscillator signal and the X2 pin is floated.                                                                                                                                 |  |  |  |  |  |  |

| 3 | 14   | ĪNTA            | Interrupt Output. When enabled, $\overline{\text{INTA}}$ is asserted low when the time/day/date matches the values set in the alarm registers. This pin is an open-drain output and requires an external pullup resistor. The pull up voltage may be up to 5.5V, regardless of the voltage on $V_{CC}$ . If not used, this pin may be left floating. |  |  |  |  |  |  |

| 4 | 15   | GND             | Ground. DC power is provided to the device on this pin.                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| 5 | 16   | SDA             | Serial Data Input/Output. SDA is the input/output pin for the I <sup>2</sup> C serial interface. The SDA pin is open-drain output and requires an external pullup resistor.                                                                                                                                                                          |  |  |  |  |  |  |

| 6 | 1    | SCL             | Serial Clock Input. SCL is used to synchronize data movement on the serial interface.                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| 7 | 2    | SQW/INTB        | Square-Wave/Interrupt Output. Programmable square-wave or interrupt output signal. It is an open-drain output and requires an external pullup resistor. The pull up voltage may be up to 5.5V, regardless of the voltage on $V_{\rm CC}$ . If not used, this pin may be left floating.                                                               |  |  |  |  |  |  |

| 8 | 3    | V <sub>CC</sub> | DC Power. DC power is provided to the device on this pin.                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| _ | 4–13 | N.C.            | No Connect. These pins are not connected internally, but must be grounded for proper operation.                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

## **TIMING DIAGRAM**

DS1337 I2C Serial Real-Time Clock

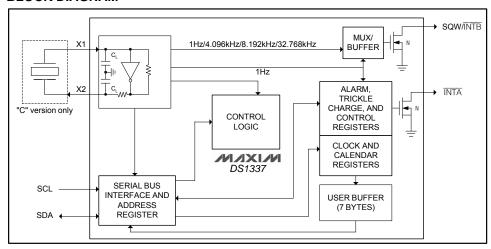

## **BLOCK DIAGRAM**

## **DETAILED DESCRIPTION**

The *Block Diagram* shows the main elements of the DS1337. As shown, communications to and from the DS1337 occur serially over an  $I^2C$  bus. The DS1337 operates as a slave device on the serial bus. Access is obtained by implementing a START condition and providing a device identification code, followed by data. Subsequent registers can be accessed sequentially until a STOP condition is executed. The device is fully accessible through the  $I^2C$  interface whenever  $V_{CC}$  is between 5.5V and 1.8V.  $I^2C$  operation is not guaranteed when  $V_{CC}$  is below 1.8V. The DS1337 maintains the time and date when  $V_{CC}$  is as low as 1.3V.

## **OSCILLATOR CIRCUIT**

The DS1337 uses an external 32.768kHz crystal. The oscillator circuit does not require any external resistors or capacitors to operate. <u>Table 1</u> specifies several crystal parameters for the external crystal. The *Block Diagram* shows a functional schematic of the oscillator circuit. The startup time is usually less than 1 second when using a crystal with the specified characteristics.

Table 1. Crystal Specifications\*

| PARAMETER         | SYMBOL         | MIN | TYP    | MAX | UNITS |

|-------------------|----------------|-----|--------|-----|-------|

| Nominal Frequency | f <sub>O</sub> |     | 32.768 |     | kHz   |

| Series Resistance | ESR            |     | 50     | kΩ  |       |

| Load Capacitance  | C <sub>L</sub> |     | 6      |     | pF    |

\*The crystal, traces, and crystal input pins should be isolated from RF generating signals. Refer to Application Note 58: Crystal Considerations for Dallas Real-Time Clocks for additional specifications.

DS1337 I<sup>2</sup>C Serial Real-Time Clock

## **CLOCK ACCURACY**

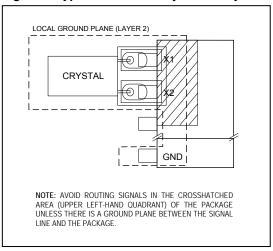

The accuracy of the clock is dependent upon the accuracy of the crystal and the accuracy of the match between the capacitive load of the oscillator circuit and the capacitive load for which the crystal was trimmed. Crystal frequency drift caused by temperature shifts creates additional error. External circuit noise coupled into the oscillator circuit can result in the clock running fast. Figure 1 shows a typical PC board layout for isolating the crystal and oscillator from noise. Refer to Application Note 58: Crystal Considerations with Dallas Real-Time Clocks for detailed information.

Figure 1. Typical PC Board Layout for Crystal

## **DS1337C ONLY**

The DS1337C integrates a standard 32,768Hz crystal in the package. Typical accuracy at nominal  $V_{CC}$  and +25°C is approximately +10ppm. Refer to *Application Note 58* for information about crystal accuracy vs. temperature.

## **OPERATING MODES**

The amount of current consumed by the DS1337 is determined, in part, by the  $I^2C$  interface and oscillator operation. The following table shows the relationship between the operating mode and the corresponding  $I_{CC}$  parameter.

| Operating Mode                                             | V <sub>cc</sub>               | Power                                       |

|------------------------------------------------------------|-------------------------------|---------------------------------------------|

| I <sup>2</sup> C Interface Active                          | 1.8V ≤ V <sub>CC</sub> ≤ 5.5V | I <sub>CC</sub> Active (I <sub>CCA</sub> )  |

| I <sup>2</sup> C Interface Inactive                        | 1.8V ≤ V <sub>CC</sub> ≤ 5.5V | I <sub>CC</sub> Standby (I <sub>CCS</sub> ) |

| I <sup>2</sup> C Interface Inactive                        | 1.3V ≤ V <sub>CC</sub> ≤ 1.8V | Timekeeping (I <sub>CCTOSC</sub> )          |

| I <sup>2</sup> C Interface Inactive<br>Oscillator Disabled | 1.3V ≤ V <sub>CC</sub> ≤ 1.8V | Data Retention                              |

DS1337 I2C Serial Real-Time Clock

## **ADDRESS MAP**

Table 2 shows the address map for the DS1337 registers. During a multibyte access, when the address pointer reaches the end of the register space (0Fh) it wraps around to location 00h. On an I<sup>2</sup>C START, STOP, or address pointer incrementing to location 00h, the current time is transferred to a second set of registers. The time information is read from these secondary registers, while the clock may continue to run. This eliminates the need to re-read the registers in case of an update of the main registers during a read.

**Table 2. Timekeeper Registers**

| ADDRESS | BIT 7   | BIT 6         | BIT 5              | BIT 4    | BIT 3               | BIT 2              | BIT 1   | BIT 0 | FUNCTION           | RANGE                    |

|---------|---------|---------------|--------------------|----------|---------------------|--------------------|---------|-------|--------------------|--------------------------|

| 00H     | 0       |               | 10 Seconds         | 5        |                     | Seconds            |         |       |                    | 00–59                    |

| 01H     | 0       |               | 10 Minutes         | i        |                     | Mini               | utes    |       | Minutes            | 00–59                    |

| 02H     | 0       | 12/24         | AM/PM<br>10 Hour   | 10 Hour  |                     | Но                 | our     |       | Hours              | 1–12<br>+AM/PM<br>00–23  |

| 03H     | 0       | 0             | 0                  | 0        | 0                   |                    | Day     |       | Day                | 1–7                      |

| 04H     | 0       | 0             | 10 [               | Date     |                     | Da                 | ate     |       | Date               | 01–31                    |

| 05H     | Century | 0             | 0                  | 10 Month |                     | Мо                 | nth     |       | Month/<br>Century  | 01–12 +<br>Century       |

| 06H     |         | 10 `          | Year               |          |                     | Ye                 | ear     |       | Year               | 00–99                    |

| 07H     | A1M1    |               | 10 Seconds Seconds |          |                     | Alarm 1<br>Seconds | 00–59   |       |                    |                          |

| 08H     | A1M2    |               | 10 Minutes         | i        | Minutes             |                    |         |       | Alarm 1<br>Minutes | 00–59                    |

| 09H     | A1M3    | 12/24         | AM/PM<br>10 Hour   | 10 Hour  |                     | Ho                 | our     |       | Alarm 1<br>Hours   | 1–12 +<br>AM/PM<br>00–23 |

| 0411    | A1M4    | DY/DT         | 10                 | Data     |                     | Da                 | ay      |       | Alarm 1<br>Day     | 1–7                      |

| 0AH     | A IW4   | וטוזט         | 101                | Jale     |                     | Da                 | ate     |       | Alarm 1<br>Date    | 01–31                    |

| 0BH     | A2M2    |               | 10 Minutes         | i        |                     | Min                | utes    |       | Alarm 2<br>Minutes | 00–59                    |

| 0CH     | A2M3    | <b>12</b> /24 | AM/PM<br>10 Hour   | 10 Hour  |                     | Hour               |         |       |                    | 1–12 +<br>AM/PM<br>00–23 |

|         |         |               |                    |          | Day                 |                    |         |       | Alarm 2<br>Day     | 1–7                      |

| 0DH     | A2M4    | DY/DT         | 10 1               | Date     | Date                |                    |         |       | Alarm 2<br>Date    | 01–31                    |

| 0EH     | EOSC    | 0             | 0                  | RS2      | RS1 INTCN A2IE A1IE |                    | Control | _     |                    |                          |

| 0FH     | OSF     | 0             | 0                  | 0        | 0                   | 0                  | A2F     | A1F   | Status             | _                        |

$\textbf{Note:} \ \textit{Unless otherwise specified, the state of the registers is not defined when power is first applied or V_{CC} falls below the V_{OSC}.$

## I<sup>2</sup>C INTERFACE

The  $l^2$ C interface is accessible whenever  $V_{\text{CC}}$  is at a valid level. If a microcontroller connected to the DS1337 resets while reading from the DS1337 during an  $l^2$ C read, the two could become unsynchronized. The microcontroller must terminate the last byte read with a Not-Acknowledge (NACK) to properly terminate the read. When the microcontroller resets, the DS1337  $l^2$ C interface may be placed into a known state by toggling SCL until SDA is observed to be at a high level. At that point the microcontroller should pull SDA low while SCL is high, generating a START condition.

DS1337 I2C Serial Real-Time Clock

### **CLOCK AND CALENDAR**

The time and calendar information is obtained by reading the appropriate register bytes. The RTC registers are illustrated in <u>Table 2</u>. The time and calendar are set or initialized by writing the appropriate register bytes. The contents of the time and calendar registers are in the binary-coded decimal (BCD) format.

The day-of-week register increments at midnight. Values that correspond to the day of week are user-defined but must be sequential (i.e., if 1 equals Sunday, then 2 equals Monday, and so on.). Illogical time and date entries result in undefined operation.

When reading or writing the time and date registers, secondary (user) buffers are used to prevent errors when the internal registers update. When reading the time and date registers, the user buffers are synchronized to the internal registers on any start or stop and when the register pointer rolls over to zero.

The countdown chain is reset whenever the seconds register is written. Write transfers occur on the acknowledge pulse from the device. To avoid rollover issues, once the countdown chain is reset, the remaining time and date registers must be written within 1 second. The 1Hz square-wave output, if enable, transitions high 500ms after the seconds data transfer, provided the oscillator is already running.

The DS1337 can be run in either 12-hour or 24-hour mode. Bit 6 of the hours register is defined as the 12- or 24-hour mode-select bit. When high, the 12-hour mode is selected. In the 12-hour mode, bit 5 is the  $\overline{\text{AM}/\text{PM}}$  bit with logic high being PM. In the 24-hour mode, bit 5 is the second 10-hour bit (20–23 hours). All hours values, including the alarms, must be reinitialized whenever the  $12/\overline{24}$ -hour mode bit is changed. The century bit (bit 7 of the month register) is toggled when the years register overflows from 99–00.

## **ALARMS**

The DS1337 contains two time-of-day/date alarms. Alarm 1 can be set by writing to registers 07h–0Ah. Alarm 2 can be set by writing to registers 0Bh–0Dh. The alarms can be programmed (by the INTCN bit of the control register) to operate in two different modes—each alarm can drive its own separate interrupt output or both alarms can drive a common interrupt output. Bit 7 of each of the time-of-day/date alarm registers are mask bits (Table 2). When all of the mask bits for each alarm are logic 0, an alarm only occurs when the values in the timekeeping registers 00h–06h match the values stored in the time-of-day/date alarm registers. The alarms can also be programmed to repeat every second, minute, hour, day, or date. Table 3 shows the possible settings. Configurations not listed in the table result in illogical operation.

The  $DY/\overline{DT}$  bits (bit 6 of the alarm day/date registers) control whether the alarm value stored in bits 0–5 of that register reflects the day of the week or the date of the month. If  $DY/\overline{DT}$  is written to logic 0, the alarm is the result of a match with date of the month. If  $DY/\overline{DT}$  is written to logic 1, the alarm is the result of a match with day of the week

When the RTC register values match alarm register settings, the corresponding alarm flag (A1F or A2F) bit is set to logic 1. The bit(s) will remain at a logic 1 until written to a logic 0 by the user. If the corresponding alarm interrupt enable (A1IE or A2IE) is also set to logic 1, the alarm condition activates one of the interrupt output (INTA or SQW/INTB) signals. The match is tested on the once-per-second update of the time and date registers.

DS1337 I<sup>2</sup>C Serial Real-Time Clock

### **Table 3. Alarm Mask Bits**

| DY/DT | ALAF | RM 1 REGIS<br>(BI | TER MASK<br>T 7) | BITS | ALARM RATE                                         |  |  |  |

|-------|------|-------------------|------------------|------|----------------------------------------------------|--|--|--|

|       | A1M4 | A1M3              | A1M2             | A1M1 |                                                    |  |  |  |

| Х     | 1    | 1                 | 1                | 1    | Alarm once per second                              |  |  |  |

| Х     | 1    | 1                 | 1                | 0    | Alarm when seconds match                           |  |  |  |

| Х     | 1    | 1                 | 0                | 0    | Alarm when minutes and seconds match               |  |  |  |

| Х     | 1    | 0                 | 0                | 0    | Alarm when hours, minutes, and seconds match       |  |  |  |

| 0     | 0    | 0                 | 0                | 0    | Alarm when date, hours, minutes, and seconds match |  |  |  |

| 1     | 0    | 0                 | 0                | 0    | Alarm when day, hours, minutes, and seconds match  |  |  |  |

| DY/DT | ALARM | 2 REGISTER MA<br>(BIT 7) | ASK BITS | ALARM RATE                                         |  |  |  |

|-------|-------|--------------------------|----------|----------------------------------------------------|--|--|--|

|       | A2M4  | A2M3                     | A2M2     |                                                    |  |  |  |

| Х     | 1     | 1                        | 1        | Alarm once per minute (00 seconds of every minute) |  |  |  |

| Х     | 1     | 1                        | 0        | Alarm when minutes match                           |  |  |  |

| Х     | 1     | 0                        | 0        | Alarm when hours and minutes match                 |  |  |  |

| 0     | 0     | 0                        | 0        | Alarm when date, hours, and minutes match          |  |  |  |

| 1     | 0     | 0                        | 0        | Alarm when day, hours, and minutes match           |  |  |  |

## **SPECIAL-PURPOSE REGISTERS**

The DS1337 has two additional registers (control and status) that control the RTC, alarms, and square-wave output.

## Control Register (0Eh)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 Bit 1 |      | Bit 0 |  |

|-------|-------|-------|-------|-------|-------------|------|-------|--|

| EOSC  | 0     | 0     | RS2   | RS1   | INTCN       | A2IE | A1IE  |  |

Bit 7: Enable Oscillator (EOSC). This active-low bit when set to logic 0 starts the oscillator. When this bit is set to logic 1, the oscillator is stopped. This bit is enabled (logic 0) when power is first applied.

Bits 4 and 3: Rate Select (RS2 and RS1). These bits control the frequency of the square-wave output when the square wave has been enabled. The table below shows the square-wave frequencies that can be selected with the RS bits. These bits are both set to logic 1 (32kHz) when power is first applied.

## SQW/INTB Output

|       | .,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |     |                    |      |  |  |  |  |  |  |  |

|-------|----------------------------------------|-----|--------------------|------|--|--|--|--|--|--|--|

| INTCN | RS2                                    | RS1 | SQW/INTB<br>OUTPUT | A2IE |  |  |  |  |  |  |  |

| 0     | 0                                      | 0   | 1Hz                | X    |  |  |  |  |  |  |  |

| 0     | 0                                      | 1   | 4.096kHz           | X    |  |  |  |  |  |  |  |

| 0     | 1                                      | 0   | 8.192kHz           | Х    |  |  |  |  |  |  |  |

| 0     | 1                                      | 1   | 32.768kHz          | X    |  |  |  |  |  |  |  |

| 1     | Х                                      | Х   | A2F                | 1    |  |  |  |  |  |  |  |

Bit 2: Interrupt Control (INTCN). This bit controls the relationship between the two alarms and the interrupt output pins. When the INTCN bit is set to logic 1, a match between the timekeeping registers and the alarm 1 registers I activates the INTA pin (provided that the alarm is enabled) and a match between the timekeeping registers and the alarm 2 registers activates the SQW/INTB pin (provided that the alarm is enabled). When the INTCN bit is set to logic 0, a square wave is output on the SQW/INTB pin. This bit is set to logic 0 when power is first applied.

DS1337 I2C Serial Real-Time Clock

Bit 1: Alarm 2 Interrupt Enable (A2IE). When set to logic 1, this bit permits the alarm 2 flag (A2F) bit in the status register to assert INTA (when INTCN = 0) or to assert SQW/INTB (when INTCN = 1). When the A2IE bit is set to logic 0, the A2F bit does not initiate an interrupt signal. The A2IE bit is disabled (logic 0) when power is first applied.

Bit 0: Alarm 1 Interrupt Enable (A1IE). When set to logic 1, this bit permits the alarm 1 flag (A1F) bit in the status register to assert  $\overline{\text{INTA}}$ . When the A1IE bit is set to logic 0, the A1F bit does not initiate the  $\overline{\text{INTA}}$  signal. The A1IE bit is disabled (logic 0) when power is first applied.

## Status Register (0Fh)

| Bit 7 | Bit 6 | Bit 6 Bit 5 Bit 4 Bit 3 Bit |   | Bit 2 | Bit 1 | Bit 0 |     |

|-------|-------|-----------------------------|---|-------|-------|-------|-----|

| OSF   | 0     | 0                           | 0 | 0     | 0     | A2F   | A1F |

**Bit 7: Oscillator Stop Flag (OSF).** A logic 1 in this bit indicates that the oscillator either is stopped or was stopped for some period of time and may be used to judge the validity of the clock and calendar data. This bit is set to logic 1 anytime that the oscillator stops. The following are examples of conditions that can cause the OSF bit to be set:

- 1) The first time power is applied.

- 2) The voltage present on  $V_{\text{CC}}$  is insufficient to support oscillation.

- 3) The  $\overline{EOSC}$  bit is turned off.

- 4) External influences on the crystal (e.g., noise, leakage, etc.).

This bit remains at logic 1 until written to logic 0.

Bit 1: Alarm 2 Flag (A2F). A logic 1 in the alarm 2 flag bit indicates that the time matched the alarm 2 registers. This flag can be used to generate an interrupt on either INTA or SQW/INTB depending on the status of the INTCN bit in the control register. If the INTCN bit is set to logic 0 and A2F is at logic 1 (and A2IE bit is also logic 1), the INTA pin goes low. If the INTCN bit is set to logic 1 and A2F is logic 1 (and A2IE bit is also logic 1), the SQW/INTB pin goes low. A2F is cleared when written to logic 0. This bit can only be written to logic 0. Attempting to write to logic 1 leaves the value unchanged.

Bit 0: Alarm 1 Flag (A1F). A logic 1 in the alarm 1 flag bit indicates that the time matched the alarm 1 registers. If the A1IE bit is also logic 1, the INTA pin goes low. A1F is cleared when written to logic 0. This bit can only be written to logic 0. Attempting to write to logic 1 leaves the value unchanged.

DS1337 I2C Serial Real-Time Clock

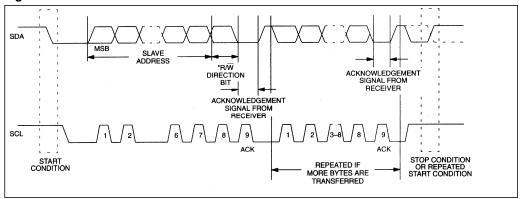

## I<sup>2</sup>C SERIAL DATA BUS

The DS1337 supports the  $l^2C$  bus protocol. A device that sends data onto the bus is defined as a transmitter and a device receiving data as a receiver. The device that controls the message is called a master. The devices that are controlled by the master are referred to as slaves. A master device that generates the serial clock (SCL), controls the bus access, and generates the START and STOP conditions must control the bus. The DS1337 operates as a slave on the  $l^2C$  bus. Within the bus specifications a standard mode (100kHz maximum clock rate) and a fast mode (400kHz maximum clock rate) are defined. The DS1337 works in both modes. Connections to the bus are made through the open-drain I/O lines SDA and SCL.

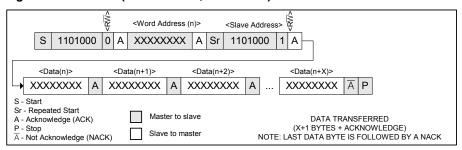

The following bus protocol has been defined (Figure 2):

- Data transfer may be initiated only when the bus is not busy.

- During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is HIGH are interpreted as control signals.

Accordingly, the following bus conditions have been defined:

Bus not busy: Both data and clock lines remain HIGH.

Start data transfer: A change in the state of the data line, from HIGH to LOW, while the clock is HIGH, defines a START condition.

Stop data transfer: A change in the state of the data line, from LOW to HIGH, while the clock line is HIGH, defines the STOP condition.

**Data valid:** The state of the data line represents valid data when, after a START condition, the data line is stable for the duration of the HIGH period of the clock signal. The data on the line must be changed during the LOW period of the clock signal. There is one clock pulse per bit of data.

Each data transfer is initiated with a START condition and terminated with a STOP condition. The number of data bytes transferred between START and STOP conditions are not limited, and are determined by the master device. The information is transferred byte-wise and each receiver acknowledges with a ninth bit.

**Acknowledge:** Each receiving device, when addressed, is obliged to generate an acknowledge after the reception of each byte. The master device must generate an extra clock pulse that is associated with this acknowledge bit.

A device that acknowledges must pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge-related clock pulse. Of course, setup and hold times must be taken into account. A master must signal an end of data to the slave by not generating an acknowledge bit on the last byte that has been clocked out of the slave. In this case, the slave must leave the data line HIGH to enable the master to generate the STOP condition.

DS1337 I2C Serial Real-Time Clock

Figure 2. Data Transfer on I<sup>2</sup>C Serial Bus

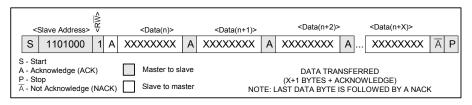

Depending upon the state of the R/W bit, two types of data transfer are possible:

- Data transfer from a master transmitter to a slave receiver. The first byte transmitted by the master is the slave address. Next follows a number of data bytes. The slave returns an acknowledge bit after each received byte. Data is transferred with the most significant bit (MSB) first.

- 2) Data transfer from a slave transmitter to a master receiver. The master transmits the first byte (the slave address). The slave then returns an acknowledge bit, followed by the slave transmitting a number of data bytes. The master returns an acknowledge bit after all received bytes other than the last byte. At the end of the last received byte, a "not acknowledge" is returned. The master device generates all of the serial clock pulses and the START and STOP conditions. A transfer is ended with a STOP condition or with a repeated START condition. Since a repeated START condition is also the beginning of the next serial transfer, the bus is not released. Data is transferred with the most significant bit (MSB) first.

The DS1337 can operate in the following two modes: